Two papers from the Computational Nanoelectronics group accepted at SC25!

Two new works co-authored by the Computational Nanoelectronics group over the past year have been accepted for presentation at the International Conference on High Performance Computing, Networking, Storage, and Analysis (SC25)! The conference accepted 136 papers overall, resulting in an acceptance rate of 21.2%.

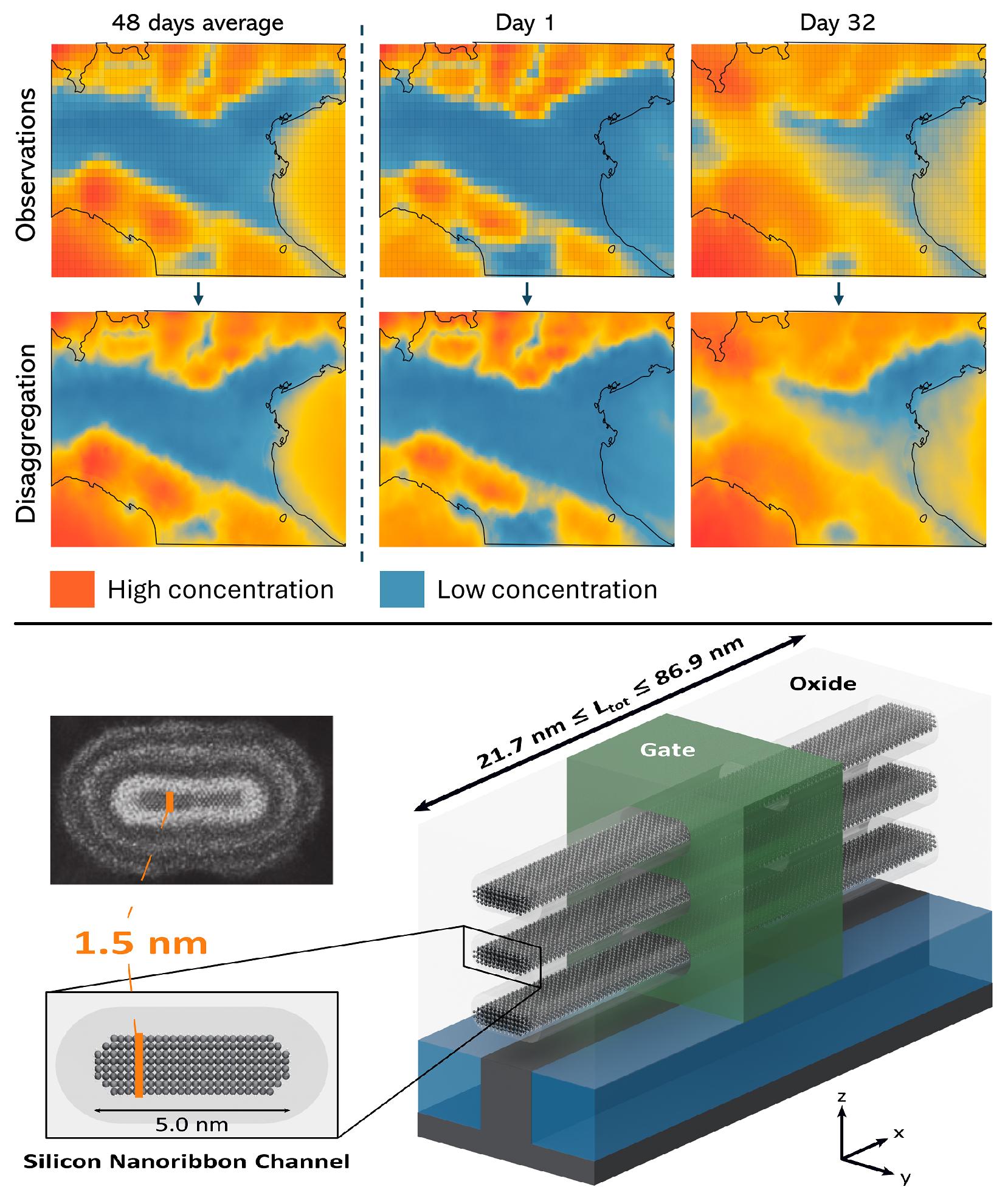

The first work is a collaboration with the Bayesian Computational Statistics and Modeling (BAYESCOMP) research group at KAUST. It presents DALIA, a new highly scalable framework for performing Bayesian inference tasks on spatio-temporal multivariate Gaussian processes (GPs), based on the methodology of integrated nested Laplace approximations (INLA). The work demonstrates that DALIA outperforms the current state of the art, R-INLA, by 2-3 orders of magnitude on a trivariate coregional model, while operating on an 8-times larger temporal domain, running on up to 496 GH200 superchips on the Alps supercomputer.

The second work is a collaboration with the Scalable Parallel Computing Lab (SPCL) at ETH Zurich. It extends last year's work on electron-electron interactions in gate-all-around (GAA) silicon nanowire transistors, using the self-consistent GW approximation implemented within a non-equilibrium Green's Function (NEGF) solver, to new scales. The updated QuaTrEx framework was used to simulate transistors made of up to 42,240 atoms on the Alps supercomputer. At the same time, it achieved sustained performance of 1 Eflop/s and 80% weak scaling efficiency on 9400 nodes of the Frontier supercomputer.

Congratulations to all co-authors involved!: Lisa Gaedke-Merzhäuser, Vincent Maillou, Fernando Rodriguez Avellaneda, Olaf Schenk, Paula Moraga, Håvard Rue, Nicolas Vetsch, Alexander Maeder, Anders Winka, Jiang Cao, Grzegorz Kwasniewski, Leonard Deuschle, Torsten Hoefler, Alexandros Nikolaos Ziogas, and Mathieu Luisier.